## **OBJECTIVE**

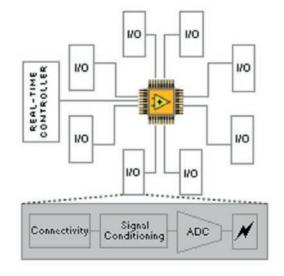

The new UC75 is a new plate-form including real time targets able to improve the performances of the control techniques of the actuators. The UC75 includes a National Instrument Core based on Compact RIO@NI and the power of the Labview@NI Libraries to control any system with fast ticks with deterministic time. The NI CompactRIO programmable automation controller (PAC) is a low-cost reconfigurable control and acquisition system designed for applications that require high performance and reliability. The system combines an open embedded architecture with small size, extreme ruggedness, and hot-swappable industrial I/O modules. CompactRIO is powered by reconfigurable I/O (RIO) FPGA technology.

The native parallelism of graphical programming is an ideal counterpart to the physical implementation of FPGAs since parallel loops map to separate regions of FPGA silicon and operate truly in parallel.

The net sum is that speed, parallelism and power of FPGAs are now accessible to anyone and this presents a powerful plateform for implementing control loop with fast parallel process as tracking servo, all running with absolute timing determinacy to drive and control the **CEDRAT TECHNOLOGIES**'s actuators. The Real time UC75 can be connected to a host to analyse in real time the behavior of the system, to adjust the parameters of the loops via an Ethernet links at 100Mbytes/s or to be stand alone with any action on the process.

In Labview RealTime, subroutines and users controls are represented by icons and the flow of data are depicted as wires called G code. The G is a dataflow language, meaning it can be conceptually represented as a directed graph of the data flowing between operations. The program execution is determined by the graphical block diagram on which programs are implemented by connecting multiple function nodes with connection wires that represent data flow between the functions.

This embedded controller can be added on the standard of the piezoelectric drivers to control with standard feedback loop or hybrid feedback/feed-forward loops or fitted toyour application via an dedicated open user-interface to control any system.

## PERFORMANCE

Typical performances are given in the following tables.

Results of tests used 1,4 channels and include only acquisition and generation of signals (T1) or Acquisition + PID + Generation of signals (T2). For these tests, the hardware and software are:

• NI cRI0-9012: Real time controller ; 400Mhz Power PC processor ; 64MB RAM

- NI cRIO-9263: 4 channels, 100kS/s, 16bit, +/-10V, Simultaneous-Update Analog Output Module

- NI CRIO-9201: 8 channels, 500kS/s, 12bit Analog input Module

Labview Real time 8.2

- NI-RIO drivers for Reconfigurable I/O in Labview FPGA (Host)

- NI-RIO FPGA Communications Framework 2.2.0 (real-Time Controller)

- NI-VISA 4.0

- NI-VISA Server 4.0

## **APPLICATIONS**

The new UC75 based on flexible plate-form from National instrument can be used to control position loop and tracking servo with high speed via CEDRAT TECHNOLOGIES's specific libraries supporting PID controller with low pass filter – Notch filter.

In addition, control of vibration can be implemented to use the power of embedded real time controllers, fast actuators and high power drivers to control your loop. With this new package, engineers may design their own control loop based on predefined libraries from CEDRAT TECHNOLOGIES or their own hardware to control their mechatronic systems with the power of Labview Real time.

This new controller can be directly connected in the rack 75 series or compatible with the CSPA driver for magnetic actuator.

| REFERENCES | UNIT    | 1 CHANNEL   | 2 CHANNELS  |

|------------|---------|-------------|-------------|

| > Notes    |         | Preliminary | Preliminary |

| Test 1 (a) | kHz     | 35.6        | 27          |

| Test 2 (a) | kHz35.6 | 25.6        | 8           |

| REFERENCES            | UNIT                                                                                         | 1 CHANNEL   |  |

|-----------------------|----------------------------------------------------------------------------------------------|-------------|--|

| > Notes               | Preliminary                                                                                  |             |  |

| Aquisition            | 4 channels 16bits +/-10V 100kS/s Simultaneous<br>Possibility 32 channels 250kS/s             |             |  |

| Generation            | 4 channels 16bits +/-10V 100kS/s Simultaneous<br>Possibility 8 channels 100kS/s Simultaneous |             |  |

| Digital Input Output  | 8 Inputs/Output 24V                                                                          |             |  |

| FPGA                  | Gates 1Million 4 slots                                                                       |             |  |

| Power consumption     | W                                                                                            | 6           |  |

| Dimensions            | mm                                                                                           | 220*100 26F |  |

| Electrical interfaces | Ethernet link 10/100Mb/s RS232 for Display, keyPad USB link for data storage                 |             |  |

## \* Note (a):

The tests were written such that all data acquired through the FPGA modules/board was transferred to the real-time controller for processing. An alternative approach for tests is to perform all the processing directly on the FPGA. This approach can achieve much faster loop rates than the numbers shown the respective table. Single channel PID calculation on the C-RIO approach 150kHz and are mainly limited by the performance of the A/D chips.